# Low-Temperature Molecular Vapor Deposition of Ultrathin Metal Oxide Dielectric for Low-Voltage Vertical Organic Field Effect Transistors

Ariel J. Ben-Sasson,<sup>†</sup> Guy Ankonina,<sup>‡</sup> Michael Greenman,<sup>†</sup> Michael T. Grimes,<sup>§</sup> and Nir Tessler<sup>\*,†</sup>

<sup>†</sup>Sara and Moshe Zisapel Nano-Electronic Center, Department of Electrical Engineering, Technion—Israel Institute of Technology, Haifa 32000, Israel

<sup>‡</sup>Photovoltaic lab, Department of Electrical Engineering, Technion—Israel Institute of Technology, Haifa 32000, Israel

<sup>§</sup>Applied Microstructures, Inc., 1020 Rincon Circle, San Jose, California 95131, United States

**Supporting Information**

**ABSTRACT:** We demonstrate a low-temperature layer-by-layer formation of a metal-oxide-only (AlO<sub>x</sub>) gate dielectric to attain low-voltage operation of a self-assembly based vertical organic field effect transistor (VOFET). The AlO<sub>x</sub> deposition method results in uniform films characterized by high quality dielectric properties. Pin-hole free ultrathin layers with thicknesses ranging between 1.2 and 24 nm feature bulk dielectric permittivity,  $\varepsilon_{AlOx}$ , of 8.2, high breakdownfield (>8 MV cm<sup>-1</sup>), low leakage currents (<10<sup>-7</sup>A cm<sup>-2</sup> at 3MV cm<sup>-1</sup>), and high capacitance (up to 1  $\mu$ F cm<sup>-2</sup>). We show the benefits of the tunable surface properties of the oxide-only dielectric utilized

here, in facilitating the subsequent nanostructuring steps required to realize the VOFET patterned source electrode. Optimal wetting properties enable the directional block-copolymer based self-assembly patterning, as well as the formation of robust and continuous ultrathin metallic films. Supported by computer modeling, the vertical architecture and the methods demonstrated here offer a simple, low-cost, and free of expensive lithography route for the realization of low-voltage ( $V_{GS/DS} \leq 3 V$ ), low-power, and potentially high-frequency large-area electronics.

**KEYWORDS:** vertical field effect transistors, oxide dielectrics, self-assembly, thin films, vapor-deposition, flexible, conjugated polymers, organic molecules

# INTRODUCTION

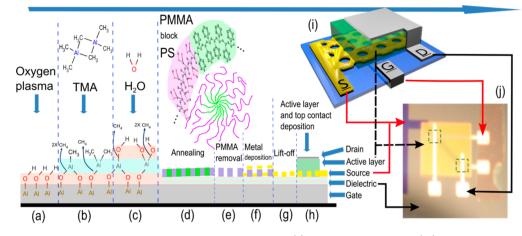

Low-power and low-voltage operation is central to organic field effect transistors (OFETs), the key enabling elements in the realization of plastic-based electronics. With the potential advantage of low-cost and large-area fabrication amenability, flexible, thin, and lightweight structure, OFETs are expected to be integrated in a variety of applications including RFID tags, flexible active matrix displays,<sup>2</sup> sensor arrays,<sup>3</sup> and disposable memory devices.<sup>4</sup> However, presently, the inherent low mobility of organic semiconductors (OSCs), compared to that of their inorganic counterparts, dictates high operating voltage and high power consumption, both of which are scarce in the typical off-grid applications. Intense research efforts aiming to overcome these limitations involve identifying new OSCs<sup>5</sup> and improved OSC morphologies,<sup>6</sup> controlling the interface chemistry of the gate dielectric,<sup>7</sup> varying structural parameters (downscaling),<sup>8</sup> and adopting different OFET architectures.<sup>9–17</sup> The patterned electrode vertical OFET (PE-VOFET), whose architecture is schematically shown in Figure 1i, is one such architecture. It offers the advantage of precise control and ease of downscaling of device critical dimensions, namely, the channel length, while remaining compatible with large area manufacturing.<sup>13,18</sup> Its inherent short channel length counterbalances the OSCs' low mobility<sup>9,19</sup> and facilitates low-power operation. Regardless, the gate bias range required to switch the device between the on and off states with standard 100 nm SiO<sub>2</sub> gate dielectric is typically large. In this work, we introduce an ultrathin, sub-10-nm thick, AlO<sub>x</sub>-only gate dielectric, using a method that belongs to the family of layer by layer self-assembly methods.<sup>20</sup> We demonstrate the integration of the deposition process with the block-copolymers self-assembly based PE-VOFET structure formation, as illustrated in the fabrication process flow in Figure 1a-h. Particularly significant is the pinhole free film structure which facilitates reliable use of high capacitance elements for large-area applications and the low-temperature deposition which confers compatibility with typical flexible substrates. Finally, we show that the above combination of design and processes facilitates realization of low-power, low-voltage, and potential high frequency devices that drive high current density through low-cost fabrication and for large-area and flexible electronics.

The gate dielectric capacitance of metal-oxide-semiconductor based transistors is described by the equation  $C = \varepsilon_0 \varepsilon_r / d$ , where

Received:November 12, 2012Accepted:March 13, 2013Published:March 13, 2013

**Figure 1.** Schematic flow of the PE-VOFET fabrication process. Left to right: (a) Remote plasma surface (Al) functionalization, (b and c) layer by layer deposition ( $H_2O$  and TMA) of AlO<sub>s</sub>, (d) block-copolymer self-assembly into vertical cylindrical structures based on the PS-b-PMMA different blocks immiscibility, (e) mask preparation, (f) metal deposition, (g) patterned electrode formation through lift-off process, (h) active layer and top contact (drain) deposition, and (i) 3D illustration of the PE-VOFET architecture. (j) Image of the structured back gate VOFET architecture.

$\varepsilon_0$ ,  $\varepsilon_r$  and d are the vacuum permittivity, the relative permittivity and the dielectric layer thickness, respectively. Hence, increased capacitance is pursued by adopting ultrathin solid-state dielectric layers, and by employing materials with dielectric constants higher than that of the traditional thermally grown SiO<sub>2</sub> ( $\varepsilon_r = 3.9$ ). Organic-only dielectric layers, such as BCB,<sup>21</sup> PVA,<sup>22</sup> PMMA,<sup>23</sup> or parylene C,<sup>24</sup> have attractive structural properties; yet these materials have low dielectric constants and impose fabrication limitations due to difficulties involving surface functionalization. Oxide dielectrics, on the other hand, are advantaged with relatively high dielectric constants and their surface can be readily functionalized by a variety of polymers, Self-Assembled-Monolayers (SAMs) or other reactive molecules. Among the various methods to obtain oxide dielectrics, the more common ones are sol-gel deposition,<sup>25</sup> metal anodization,<sup>26,27</sup> plasma-induced ultrathin oxide layer functionalized with a judicial choice of SAMs,<sup>28</sup> and the layer-by-layer self-assembly process known as atomic layer deposition (ALD).<sup>29</sup> However, obtaining large-area, pinhole free films with low leakage currents in an oxide dielectric, so far requires use of thick oxides or the additional use of organic layers (polymer/SAMs) for the ultrathin oxides.<sup>28</sup> Consequently, the overall capacitance dramatically decreases. Here we describe a layer by layer self-assembly process that is somewhat different to the common ALD process using molecular vapor deposition tool (MVD100E by Applied Microstructures, Inc.). The differences in the process result in a modified, oxygen rich, AlO<sub>x</sub> stoichiometry that is also associated with other electrical attributes. Those are the reliable, sub 10 nm pinhole free cm<sup>2</sup>scale layers, the bulk dielectric constant,  $\varepsilon_{AlOx}$ , which equals 8.2, and the improved insulating properties: High breakdown field  $(>8 \text{ MV cm}^{-1})$ , low leakage currents  $(<10^{-7} \text{ A cm}^{-2} \text{ at } 3 \text{ MV})$ cm<sup>-1</sup>), and high capacitance (up to 1  $\mu$ F cm<sup>-2</sup>). It is worth noting that the nondestructive low temperature process incorporated here to form the gate dielectric of the PE-VOFET is independent of the substrate material and thus compatible with various architectures and substrates, including flexible ones.

# RESULTS AND DISCUSSION

Like other layer-by-layer self-assembly processes, the ALD and its modifications are typically used for the formation of highly uniform SAMs employing organo-functional molecules. These are commonly utilized for the purpose of traps passivation,<sup>7</sup> free energy alignment, or energy levels alignment.<sup>30</sup> Here, employing water and the metalorganic molecule trimethylaluminium (TMA) as reactants, facilitates a layer-by-layer formation of AlO<sub>x</sub>. These coupled reactants, considered ideal for either low<sup>31,32</sup> or high temperature ALD process because of their reactivity and process stability,<sup>33</sup> are of at least similar quality when prepared using the low temperature altered ALD process as described here.

The process chemistry of  $AlO_x$  monolayer formation is similar to the common ALD process and is described by two successive "half-processes". During the first half-process, the TMA reacts with the hydrogen atoms of the surface hydroxyl groups through a ligand exchange in which an O-Al bond is formed and methane is released. The formation of highly dense and full coverage dielectric layer requires that the binding sites, hydroxyl groups, densely cover the entire surface. To this end, oxygen plasma is generated outside the chamber and injected to it to react and produce high coverage of hydroxyl groups. This is especially critical when depositing on metals, such as gold, where the formation of surface hydroxyl groups are not thermodynamically favorable<sup>34</sup> (Supporting Information, Figures S4 and S6). Following this in situ surface preparation step, a predetermined amount of the TMA molecules' vapor is injected into the reaction chamber. The driving force for the TMA injection, being the pressure difference between the TMA antechamber (1 Torr) and the reaction chamber (being held below 0.02 Torr), results in a relatively dense and uniform injection aimed to promote faster reaction with the exposed surface. The surface reaction, the ligand exchange,<sup>35</sup> involves a single hydroxyl group (eq 1a) or two hydroxyl groups simultaneously (eq 1a) and results in a methyl-terminated surface.<sup>36</sup> In the second half-process described in eq 2, H<sub>2</sub>O is introduced to the reaction chamber in the same way as described for the TMA. The H<sub>2</sub>O reacts with the methylterminated groups, releasing methane, and reconverts the surface population back to hydroxyl-terminated groups; see the process flow at Figure 1 part b and c. Thus, the H<sub>2</sub>O/TMA is a self-terminated process by nature, adding up to a single layer per cycle with an approximated thickness of 1.2 Å, 32 enabling to determine film thickness with atomic-scale accuracy, independent of reaction time or amount of reactants.

$$\|\operatorname{Al-OH} + \operatorname{Al}(\operatorname{CH}_3)_3(g)$$

$$\rightarrow \|\operatorname{Al-O-Al}(\operatorname{CH}_3)_2 + \operatorname{CH}_4(g)$$

(1a)

$2 \parallel O - H + Al(CH_3)_3 (g) \rightarrow (\parallel O - )_2 AlCH_3 + 2CH_4 (g)$ (1b)

$$\|\operatorname{Al-CH}_{3} + \operatorname{H}_{2}O(g) \rightarrow \|\operatorname{Al-OH} + \operatorname{CH}_{4}(g)$$

(2)

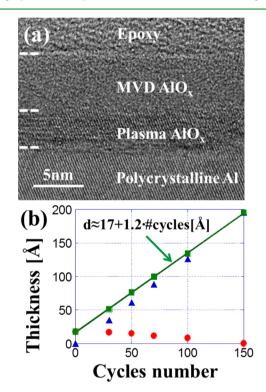

To deduce on the quality of the modified ALD process and the resulting film characteristics we initially examined the layer structural properties using high-resolution transmission electron microscopy (HRTEM). Films were covered by epoxy as part of the TEM sample preparation procedure. The HRTEM micrograph of 50-deposition-cycles film, shown in Figure 2a,

**Figure 2.** (a) HRTEM cross section of an AlO<sub>x</sub>-MVD deposited film. (b) Ellipsometry measurement distinguishing the oxygen plasma induced AlO<sub>x</sub> (circles) and the MVD-deposited AlO<sub>x</sub> (triangles).The sum of both is indicated with squares.

reveals three distinct layers under the epoxy cover. The first two lower layers are the thermally deposited polycrystalline aluminum substrate and the overlaying oxidized region, the latter partly formed during the predeposition plasma exposure. The oxidized Al region is distinguishable as it preserves some of the crystallinity of the aluminum film. The third layer is the MVD100E tool-deposited AlO<sub>x</sub> film which appears to be amorphous as is common to low temperature deposition processes. An important use of the HRTEM images is to accurately calibrate the ellipsometry measurements. To this end we examined the cross sections of a second film, 100-deposition-cycles thick, to fix two points on the ellipsometry scale. The extracted films thickness for the 50- and 100-cycles films were 5.9  $\pm$  0.4 and 12  $\pm$  0.4 nm, respectively, with an additional 2  $\pm$  0.5 nm of plasma oxidized alumina.

The HRTEM-calibrated ellipsometry measurements of samples prepared at 60 °C, shown in Figure 2b, confirm the linearity of the film growth process (square symbols). We note that the process may also be performed at lower temperatures, and a range of samples prepared at temperatures between 40 and 100 °C demonstrated similar properties (not shown here). Using ellipsometry one can also attempt to differentiate between the crystalline and amorphous films and extract their thickness individually (triangles and round symbols in Figure 2b). However, this procedure failed for the thick alumina layers where it could not reproduce the ~2 nm crystalline alumina that was clearly evident in the HRTEM images. The average values obtained by fitting the linear slope are 17 Å of oxidized aluminum and a growth rate of 1.2 Å/cycle, in agreement with literature predicted values.<sup>32</sup>

After establishing the structural characterization and quality of the layers when grown on Al substrates, we turned to explore their electrical properties. To this end we measured leakage current, breakdown field, and capacitance using a metal—insulator—metal (MIM) configuration. The structure was prepared by first depositing a large area aluminum film on a glass substrate followed by the above layer by layer process to grow the desired AlO<sub>x</sub> film thickness. Finally, a top aluminum layer was deposited (thermal evaporation) through a shadow mask resulting in several capacitors on a given substrate (see Supporting Information, Figure S2). To ensure reliable interpretation of the measured data we tested very different capacitor areas ( $10^{-4}$  cm<sup>2</sup> and  $2.52 \times 10^{-2}$  cm<sup>2</sup>) and in some of the samples we also replaced either the top or bottom aluminum electrode with gold.

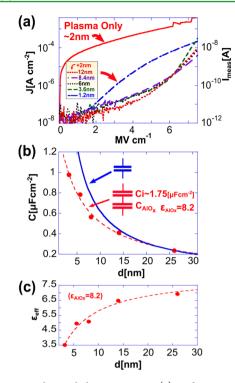

Figure 3a presents the leakage current density as a function of applied electric field obtained for AlO<sub>x</sub> layer thicknesses, which, according to Figure 2b, correspond to values between ~29 and ~137 Å. We also added the result obtained for the oxidized aluminum only (~17 Å thick). To compare the different thicknesses and observe potentially enhanced leakage or breakdown in the thinnest films, we plotted the current as a function of electric field and not bias voltage. But for the oxidized aluminum-only layer, all other capacitors showed good insulating properties which are similar up to 7.5 MV cm<sup>-1</sup>. We note that the thinnest layer, with layer by layer deposited thickness of 12 Å (+~17 Å oxidized aluminum) demonstrated somewhat higher leakage currents but similar robustness toward breakdown. The breakdown electric field (not shown) was slightly above 8 MV cm<sup>-1</sup>. However, for the application considered here, 3 MV cm<sup>-1</sup> is already a high enough electric field and is equivalent to about 60 V across 100 nm SiO<sub>2</sub> film. The similarity between the leakage curves points toward the very good insulating properties of the layers. In the literature such good insulating properties of oxide layers are associated with low density of oxygen vacancies,<sup>37</sup> an effect that is supported by the layers' stoichiometry,  $Al_2O_x$  (x > 3), obtained by XPS bulk measurements (Supporting Information, Figure S5).

Turning to the capacitance measurements, the round symbols in Figure 3b show the capacitance as a function of the layer thickness (d). As described in the Supporting Information capacitance was deduced from both voltage and frequency-dependent capacitance measurements, where the values presented correspond to the high frequency (1 MHz to 1 kHz) capacitance (Supporting Information, Figure S3). The solid line in Figure 3b represents the 1/d dependence expected from an ideal capacitor, and it clearly shows that the data

Figure 3. MIM electrical characterization. (a) Leakage current density as function of applied electric field; the indicated thicknesses do not include the additional plasma induced oxide layer with the approximated thickness of 17 Å. (b) Capacitance measurements (red circles), and the fit (dashed line) to the serial capacitance model, compared to the ideal model of a single capacitor (solid line). (c) Effective permittivity as function of insulator thickness.

cannot be reproduced by an ideal single capacitor. The analysis of thin and ultrathin parallel plate capacitors often deviates from the classical analysis, which follows 1/d and theoretically approaches infinity capacitance as thickness is reduced. The reasons for this deviation can be attributed to quantum effects<sup>38,39</sup> at the metal—insulator interface or to the formation of an interfacial layer which introduce yet another capacitor in series.<sup>34,40,41</sup> The inclusion of interface capacitance is abundant in analyses of capacitors films when their thickness ranges between 2 nm and 25 nm. In such a case the measured capacitance,  $C_{\text{meas}}$ , is said to be composed of both the interface capacitance,  $C_{ij}$  and the film capacitance according to

$$1/C_{\text{meas}} = 1/C_{\text{i}} + d/\varepsilon_{\text{AlO}_{x}}\varepsilon_{0}$$

(3)

In eq 3, *d* is the insulator thickness and  $\varepsilon_0$  is the vacuum permittivity. Following previous works on thin films,<sup>40</sup> we fitted the experimental values to eq 3, dashed line, resulting in an interface capacitance of  $C_i = 1.75[\mu \text{F cm}^{-2}]$  and bulk dielectric constant of  $\varepsilon_{\text{AlO}_x} = 8.2$ . For completeness, we note that the results in Figure 3b can also be reproduced by an effective dielectric constant that decreases for thinner films, see Figure 3c. In Figure S4 of the Supporting Information, we show that the measured capacitance is dependent on the type of metal used for the capacitor plate and hence we favor the interpretation through the existence of a serial interface capacitor. Regardless of the mechanism at hand it places another scaling limit on reducing the dielectric film thickness.

Before presenting the effect of the thin  $AlO_x$  on the VOFET performance, we briefly discuss the architecture and operation of such FETs so that the structural and functional roles of the

gate dielectric are better understood. As shown in Figure 1, in the VOFET architecture, the layers are vertically stacked. The spacing between the source and the drain, which defines the channel length, is determined by the OSC thickness, a parameter easily downscaled in fabrication. Featuring intrinsically short channel length, the VOFET is able to drive high current density under low applied drain bias. Thus, it offers a facile fabrication method for low-power devices. However, the physical principles underlying the VOFET behavior differ from those of lateral FETs.<sup>19,42</sup> As previously described in ref 42 and recently discussed in depth in ref 18, the channel, being vertical, is not directly influenced by the gate. Instead, the gate alters the charge injection properties of the source-OSC interface. When unbiased, the source-OSC Schottky barrier dominates the current between the source and the drain. The current can then be described similarly to the current at a contact limited (CL) diode. By applying gate bias, the resulting electric field induces a potential barrier lowering, ultimately resulting in space charge limited (SCL) conduction (ref 19 section IV.E). The gate influence penetrates its way to the source-OSC interface region through gaps in the metallic patterned electrode (see Figure 1i), which would have been otherwise completely screened because of the atomic length of the Debye shielding in metals.<sup>43</sup> Taking a closer look at the mechanism that facilitates this switching behavior,<sup>18</sup> we note that the potential barrier lowering induces charge accumulation at the patterned source electrode perforations. As the charge injection into the channel is confined within the perforations, both it and the electric field screening are greatly affected by the patterned electrode perforations' (also referred to as "tunnels") aspect ratio through the so-called "tunnel effect".<sup>42</sup> It is worth noting that gate screening effects by the source electrode, are more dominant in the vertical configuration than in the lateral one, a fact that stands behind the original design of the perforated source electrode.<sup>44</sup> Still, minimizing the gate screening and increasing the gate's capacitance bear consequence on important functional parameters, such as the subthreshold swing. In previous work, we dealt with the patterned electrode screening effects<sup>18,19</sup> and have shown that it is necessary to realize an ultrathin and smooth patterned electrodes with determined perforation diameter size, for practical use (see Supporting Information of ref 32, Figures S2 and S3). In this study, we keep the patterned electrode design fixed, and concentrate on the influence of the gate capacitance.

We demonstrate the gate capacitance effect by comparing two structures, one with a standard bottom gate, 100 nm thermal grown SiO<sub>2</sub> dielectric, and a second, which has a structured bottom gate and ~8 nm AlO<sub>x</sub> dielectric. An image of a structured back gate VOFET is shown in Figure 1j. As mentioned above, to isolate the effect of the dielectric thickness reduction, and thus mostly the effect of the increased dielectric capacitance, the remaining of the structure was kept the same. To that end, we rely on the fabrication process in which the perforations' aspect ratio is determined through blockcopolymer (BCP) based self-assembly and lift-off processes. These processes are schematically shown in Figure 1 steps d through g and are thoroughly described in refs 9 and 18.

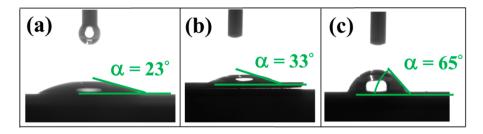

The deposition of ultrathin BCP solution to result in the required pattern formation<sup>45</sup> is directly related to the substrate surface energy, that is, its hydrophilic/hydrophobic nature. The as-deposited  $AlO_x$  contact angle with H<sub>2</sub>O and the one reached at steady state after a number of days are 23° and 33°, respectively (see Figure 4a and b and ref 46). These values

Figure 4.  $H_2O$  contact angle measurements: (a) bare  $AlO_x$  layer immediately after deposition, (b) bare  $AlO_x$  layer 3 days after deposition, and (c) after hydrophobic solutions treatment.

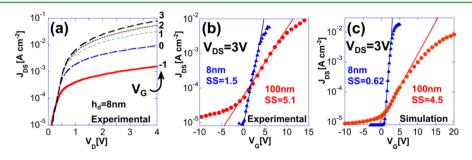

**Figure 5.** VOFET operational characterization. (a) Output characteristics  $(J_D-V_{DS})$  of the MVD dielectric based VOFET. (b) Comparison of the transfer characteristics  $(J_D-V_{GS})$  of the two structures: MVD dielectric-based (triangles) and 100 nm SiO<sub>2</sub>-based (circles) PE-VOFET. (c) Simulation comparison between the transfer characteristics of two VOFETs with different dielectric thicknesses.

indicate a very hydrophilic surface which would cause dewetting of the hydrophobic BCP solution and thus prevent the formation of the required thin (sub 50 nm) films. Tuning this value to be compatible with the BCP self-assembly process is done through soaking the substrate in hydrophobic solutions such as acetone resulting in an increased contact angle of 65° (Figure 4c). Through this method, the obtained perforation diameters were approximately 80 and 60 nm, over SiO<sub>2</sub> and AlO<sub>x</sub>, respectively.

For the purpose of metal deposition the  $AlO_x$  surface provides excellent adhesion allowing for reliable electrode formation down to below 10 nm, as required by this transistor architecture.<sup>42</sup> The good insulating properties of the AlO<sub>x</sub> produced by the modified process allowed us to avoid the often required step of covering with organic SAM and thus maintain the good adhesion of the oxide surface and thus the robustness of the metals (Ti/Au) constituting the patterned electrode to the insulating stack. This is especially important where the fabrication process relies on a lift-off process that may damage very thin metal films where adhesion is not perfect (as adhesion to SAM may be). Patterned electrodes fabricated over the oxide layer with thicknesses down to  $\sim 7$  nm demonstrate sheet resistance of ~280  $\Omega$  sq^-1, which decreases to ~110  $\Omega$  sq<sup>-1</sup>, when the thickness increases to ~9 nm (details on the patterned electrodes thickness vs transparency and conductivity are available in ref 18)

To complete the device structure, 500 nm  $C_{60}$  fullerene and top Al drain contact are used with the two platforms, the one with the SiO<sub>2</sub> and the one with the AlO<sub>x</sub> dielectric. Pin-hole formation in the fullerene film prevents further thickness downscaling (this probably because of the effect of the modulated perforated surface on the semicrystalline C60 film). However, one can use amorphous semiconductors, as was shown in ref 13, demonstrating reliable structures with sub-100-nm channel lengths, with the prospects of downscaling to few tens of nm. Since our focus here is on the gate dielectric, we do not include study of other semiconductor materials that would indeed allow for very thin channel lengths.

Figure 5a shows the output characteristics of the device made with the thin alumina layer. The device demonstrates switching within gate bias range of 3 V, and high driving current of over 10 mA cm<sup>-2</sup> under drain bias below 2 V. As Figure 5a and to some extent also Figure 5b shows the transistor is not OFF at zero gate bias and a negative bias is required to obtain better ON-OFF ratio. As is discussed in detail in ref 18 and 42, this is associated with nonideal alignment between the electrode work function and the C<sub>60</sub> LUMO level (i.e., too low injection barrier). Figure 5b shows the transfer characteristics of devices of the two types, being driven by source drain bias of 3 V. To quantify the difference between the performance of both we use the definition of the subthreshold slope (SS)  $[\Delta V_{GS}/\Delta \log (J_{DS})$ ]. The SS value measures the gate bias change required to increase the current between the source and the drain by one decade. The SS value is extracted from the transfer characteristics,  $\log(J_D) - V_{GS}$  plot, at the region between  $V_{OD}$  and  $V_T$ (Supporting Information, Figure S8). This value decreases from ~5.1 V/dec for 100 nm SiO<sub>2</sub>-based devices (Figure 5b, circles) to ~1.5 V/dec for the MVD-based devices (Figure 5b, triangles).

Compared to what is achieved in lateral FETs upon reducing the oxide thickness, one might expect a higher reduction in the slope by the factor of  $(d_{SiO_2}/\varepsilon_{SiO_2})/(d_{AlO_x}/\varepsilon_{eff}(d)) = 17$  instead of just 3.5. As discussed in ref 19, this is, at least in part, due to the unique architecture if the vertical device, which makes the slope or the on/off ratio limited also by the aspect ratio of the perforations (metal film thickness relative to perforation typical width). To gain some intuition as to the extent of the ideal influence of downscaling the dielectric layer thickness, we have utilized a mean field self-consistent numerical simulation prepared in MatLab. Description of the simulation is found in ref 19 and specific simulation parameters are found in the Supporting Information, Figure S7 and Table S2. Figure 5c shows the transfer characteristics obtained by the simulation for

# **ACS Applied Materials & Interfaces**

devices with 100 and 8 nm thick dielectric layers. The SS values derived from these curves (4.5 and 0.6) show a factor of 7.5, which is still significantly smaller than the factor of 17 expected based on performance of lateral FETs. There is still a difference between the experiment and the numerical results, which may be due to either the model not being able to capture all the physics (see discussion in ref 19) or due to the presence of trap states at the interface between the AlO<sub>x</sub> and the semiconductor. Further research in this direction, involving trap state passivation is required to elucidate this issue.

# CONCLUSIONS

We have presented a low temperature technique for the formation of reliable, oxide-only, pinhole free, high-k insulating layers with atomic scale thickness accuracy based on a layer-bylayer self-assembly process that is slightly modified compared to the commonly used ALD process. Regardless of the layers' thickness the leakage properties as a function of applied electric field were found to be identical, allowing the usage of ultrathin layers (sub-8-nm) with capacitance ranging between 0.5 and 1  $\mu$ F cm<sup>-2</sup>. Our initial studies of the film structure showed oxygen rich stoichiometry that may attribute to the excellent insulating properties. To demonstrate its use, we further incorporated these layers as the gate dielectric of a PE-VOFET, benefiting from the ease of controlling the dielectric's surface properties to allow the block-copolymer-based self-assembly fabrication. The PE-VOFET is intrinsically characterized by low-power consumption; through integrating the thin  $AlO_x$ layer, we demonstrated a low-power as well as low-voltage PE-VOFET as it operates under low  $V_{GS}$  bias. Considering the low temperature processes described here, we further note that this device may be readily made flexible with a simple change of substrate material. The prospects of the vertical architecture for efficient integrated circuits,<sup>13</sup> as well as the properties of the demonstrated modified layer-by-layer self-assembly AlO, dielectric for large area electronics, place them both, individually or combined, as interesting components for organic logic as these elements commence their way into commercial implementations.

## EXPERIMENTAL SECTION

Device Fabrication. Devices were fabricated over highly doped ptype silicon wafers with 100 nm, dry, chlorinated thermal oxide layer (purchased from Nova Electronics Materials), which served as the bottom gate and dielectric layer of the reference PE-VOFETs, and as the substrate for the AlO<sub>x</sub>-based VOFET. Samples were cleaned with a nitrogen gun and rinsed in acetone, methanol, and isopropanol solutions, sequentially, for 5 min each, in ultrasonic bath and finally dried over a hot plate at 110 °C. Al bottom contacts, for MIM (on glass) and VOFETs (on silicon substrates), were deposited to the thickness of 30 nm by e-gun evaporator (Temescal, FC-1800) and patterned using shadow masks. AlO<sub>x</sub> dielectric was deposited to the required thickness by a Molecular Vapor Deposition machine (MVD100E, Applied Microstructures Inc.). Prior to deposition the Al bottom gate was treated in situ with mild (remotely generated) oxygen plasma (15 s, 150 W), which was followed immediately by the MVD100E deposition process. The number of MVD100E cycles varied between 10 and 200 according to the desired film thickness. In each cycle, the reactants were vaporized and introduced into the reaction chamber for a period of 1 s before being thoroughly removed by nitrogen purging. Polystyrene (PS) masks were produced according to the procedure previously described in ref 9 using self-assembly of polystyrene-block-poly(methyl methacrylate) (PS-PMMA) diblockcopolymer (BCP) (M<sub>n</sub> 941 kDa, 33 wt % PS, purchased from Polymer Source, Inc.). Patterned source electrodes were formed by a sequential

deposition (TFDS-184, VST systems Ltd.) of a thin titanium layer (nominally 3 nm, serving as adhesion layer) and gold layer (approximately 6 nm). The metal film deposition was followed by a lift off process resulting in the patterned electrode (PE). Further PE-VOFET fabrication steps were performed in a nitrogen inert atmosphere glovebox. C<sub>60</sub> fullerene 99.9% n-type OSC (purchased from MER Corporation) was thermally evaporated over the PE under vacuum conditions of ~10<sup>-6</sup> mbar to a nominal thickness of 500 nm. Finally, Al top contact, the drain electrode, was thermally deposited on top.

**Electrical Characterization.** Leakage current measurements,  $I_D - V_D$  sweeps, were performed for the MIM analysis on several samples ( $\geq$ 5 samples from each thickness) using a Semiconductor Parameters Analyzer (SPA; Agilent 4155B). Capacitance was measured at 1 MHz on the same samples, using a capacitor analyzer (Boonton, 7200 capacitancemeter). The complex impedance was measured as a function of the frequency (from 1 MHz to 1kHz) using an AC spectroscopy system, a frequency response analyzer coupled to an electrochemical test interface (Novocontrol Alpha-AK and POT/GAL). Data was analyzed using the Zview software (Scribner Associates, Inc., U.S.A.). Electrical characterization of the PE-VOFETs was performed with Semiconductor Device Analyzer (Agilent B1500A) in a glovebox in dark.

**Structural Characterization.** PE-related fabrication steps (layers thickness, perforation diameter, etc.) and the AlO<sub>x</sub> film roughness were characterized by an AFM system (Veeco DI-3000) in tapping mode. HRTEM analysis was performed with the Titan 80–300 kV S/TEM (FEI) and served to calibrate ellipsometry measurements. HRTEM sample preparation was performed in a Gatan 691 Precision Ion Polishing System (PIPS). The AlO<sub>x</sub> thickness analysis was performed by an ellipsometry measurement (VASE, J. A. Woollam Co., Inc.). AlO<sub>x</sub> stoichiometry was measured with X-ray Photoelectron Spectroscopy (XPS; Thermo VG Scientific Sigma Probe). Surface adhesion properties were characterized through evaluation of the surface energy, based on contact angle measurements (Ramé-hart model 250 Standard Contact Angle Goniometer).

## ASSOCIATED CONTENT

### **S** Supporting Information

Details on structural characterization using AFM and XPS. The layout of the MIM configuration is shown, as well as details on the two methods used to extract capacitance values. A comparison between Al and Au electrodes at the MIM configuration is shown as well as the Au films' contact angle measurements. Computational model and simulation parameters used in this study are detailed. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

## **Corresponding Author**

\*E-mail: nir@ee.technion.ac.il.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This research was supported by the Israel Science Foundation (grant 695/10) and the Russell Berrie Nanotechnology Institute at the Technion—Israel Institute of Technology. Ariel J. Ben-Sasson is grateful to the Azrieli Foundation for the award of an Azrieli Fellowship. The authors thank Dr. Yaron Kauffmann and Mr. Michael Kalina for the TEM measurements. The authors also thank Dr. Reuven Brener for the XPS measurements. Some of the fabrication steps were performed at the Micro-Nano Fabrication Unit (MNFU) at Technion.

#### **ACS Applied Materials & Interfaces**

ABBREVIATIONS

OFET = organic field effect transistor

OSC = organic semiconductors

PE-VOFET = patterned electrode vertical organic field effect transistor

MVD = molecular vapor deposition

ALD = atomic layer deposition

TMA = trimethylaluminium

MIM = metal-insulator-metal

PE = patterned electrode

BCP = block copolymer

CL = contact limited

SCL = space charge limited

AFM = atomic force microscopy

TEM = transmission electron microscopy

#### REFERENCES

(1) Subramanian, V.; Chang, P. C.; Lee, J. B.; Molesa, S. E.; Volkman, S. K. IEEE Trans. Compon. Packag. Technol. 2005, 28 (4), 742-747.

(2) Gelinck, G. H.; Huitema, H. E. A.; van Veenendaal, E.; Cantatore, E.; Schrijnemakers, L.; van der Putten, J. B. P. H.; Geuns, T. C. T.; Beenhakkers, M.; Giesbers, J. B.; Huisman, B.-H.; Meijer, E. J.; Benito, E. M.; Touwslager, F. J.; Marsman, A. W.; van Rens, B. J. E.; de Leeuw, D. M. Nat. Mater. **2004**, 3 (2), 106–110.

(3) Sekitani, T.; Zschieschang, U.; Klauk, H.; Someya, T. Nat. Mater. **2010**, *9* (12), 1015–1022.

(4) Sekitani, T.; Yokota, T.; Zschieschang, U.; Klauk, H.; Bauer, S.; Takeuchi, K.; Takamiya, M.; Sakurai, T.; Someya, T. *Science* **2009**, 326 (5959), 1516–1519.

(5) Li, J.; Zhao, Y.; Tan, H. S.; Guo, Y.; Di, C.-A.; Yu, G.; Liu, Y.; Lin, M.; Lim, S. H.; Zhou, Y.; Su, H.; Ong, B. S. *Sci. Rep.* **2012**, *2*, 754–754.

(6) Wen, Y.; Liu, Y.; Guo, Y.; Yu, G.; Hu, W. Chem. Rev. **2011**, 111 (5), 3358–3406.

(7) Chua, L. L.; Zaumseil, J.; Chang, J. F.; Ou, E. C. W.; Ho, P. K. H.; Sirringhaus, H.; Friend, R. H. *Nature* **2005**, 434 (7030), 194–199.

(8) Zhang, Y. J.; Petta, J. R.; Ambily, S.; Shen, Y. L.; Ralph, D. C.; Malliaras, G. G. Adv. Mater. 2003, 15 (19), 1632-+.

(9) Ben-Sasson, A. J.; Avnon, E.; Ploshnik, E.; Globerman, O.; Shenhar, R.; Frey, G. L.; Tessler, N. *Appl. Phys. Lett.* **2009**, 95 (21), 213301–3.

(10) Ma, L. P.; Yang, Y. Appl. Phys. Lett. 2004, 85 (21), 5084–5086.

(11) Liu, B.; McCarthy, M. A.; Yoon, Y.; Kim, D. Y.; Wu, Z. C.; So, F.; Holloway, P. H.; Reynolds, J. R.; Guo, J.; Rinzler, A. G. Adv. Mater. 2008, 20 (19), 3605-+.

(12) Uno, M.; Nakayama, K.; Soeda, J.; Hirose, Y.; Miwa, K.; Uemura, T.; Nakao, A.; Takimiya, K.; Takeya, J. Adv. Mater. 2011, 23 (27), 3047–3051.

(13) Ben-Sasson, A. J.; Chen, Z.; Facchetti, A.; Tessler, N. Appl. Phys. Lett. 2012, 100 (26), 263306-4.

(14) Seidel, K.; Rossi, L.; Mello, R. Q.; Hümmelgen, I. J. Mater. Sci.: Mater. Electron. 2012, 1–5.

(15) Georgiou, T.; Jalil, R.; Belle, B. D.; Britnell, L.; Gorbachev, R. V.;

Morozov, S. V.; Kim, Y.-J.; Gholinia, A.; Haigh, S. J.; Makarovsky, O.; Eaves, L.; Ponomarenko, L. A.; Geim, A. K.; Novoselov, K. S.;

Mishchenko, A. Nat. Nano 2013, 8, 100-103.

(16) McCarthy, M. A.; Liu, B.; Donoghue, E. P.; Kravchenko, I.; Kim, D. Y.; So, F.; Rinzler, A. G. *Science* **2011**, 332 (6029), 570–573.

(17) Nelson, S. F.; Levy, D. H.; Tutt, L. W. Appl. Phys. Lett. 2012, 101 (18), 183503-4.

(18) Ben-Sasson, A. J.; Tessler, N. Nano Lett. 2012, 12 (9), 4729–4733.

(19) Ben-Sasson, A. J.; Tessler, N. J. Appl. Phys. 2011, 110 (4), 044501-12.

(20) Maoz, R.; Matlis, S.; DiMasi, E.; Ocko, B. M.; Sagiv, J. Nature **1996**, 384 (6605), 150–153.

(21) Chua, L.-L.; Ho, P. K. H.; Sirringhaus, H.; Friend, R. H. Appl. Phys. Lett. 2004, 84 (17), 3400-3402.

(22) Rossi, L.; Seidel, K. F.; Machado, W. S.; Hummelgen, I. A. J. Appl. Phys. 2011, 110 (9), 094508-5.

(23) Noh, Y.-Y.; Sirringhaus, H. Org. Electron. 2009, 10 (1), 174–180.

(24) Cosseddu, P.; Piras, A.; Bonfiglio, A. IEEE Trans. Electron Devices 2011, 58 (10), 3416-3421.

(25) Jeong, S.; Kim, D.; Lee, S.; Park, B.-K.; Moon, J. Appl. Phys. Lett. 2006, 89 (9), 092101-3.

(26) Majewski, L. A.; Schroeder, R.; Grell, M. J. Phys. D: Appl. Phys. 2004, 37 (1), 21.

(27) Kaltenbrunner, M.; Stadler, P.; Schwödiauer, R.; Hassel, A. W.; Sariciftci, N. S.; Bauer, S. *Adv. Mater.* **2011**, 23 (42), 4892–4896.

(28) Klauk, H.; Zschieschang, U.; Pflaum, J.; Halik, M. Nature 2007, 445 (7129), 745–748.

(29) Ho, M. Y.; Gong, H.; Wilk, G. D.; Busch, B. W.; Green, M. L.; Voyles, P. M.; Muller, D. A.; Bude, M.; Lin, W. H.; See, A.; Loomans,

M. E.; Lahiri, S. K.; Raisanen, P. I. J. Appl. Phys. 2003, 93 (3), 1477-1481.

(30) Braun, S.; Salaneck, W. R.; Fahlman, M. Adv. Mater. 2009, 21 (14–15), 1450–1472.

(31) George, S. M. Chem. Rev. 2010, 110 (1), 111-131.

(32) Groner, M. D.; Fabreguette, F. H.; Elam, J. W.; George, S. M. Chem. Mater. 2004, 16 (4), 639-645.

(33) Puurunen, R. L. J. Appl. Phys. 2005, 97 (12), No. 121301.

(34) Groner, M. D.; Elam, J. W.; Fabreguette, F. H.; George, S. M. Thin Solid Films 2002, 413 (1-2), 186-197.

(35) Yaacobi-Gross, N.; Soreni-Harari, M.; Zimin, M.; Kababya, S.; Schmidt, A.; Tessler, N. *Nat. Mater.* **2011**, *10* (12), 974–979.

(36) Dillon, A. C.; Ott, A. W.; Way, J. D.; George, S. M. Surf. Sci. 1995, 322 (1-3), 230-242.

(37) Perevalov, T. V.; Tereshenko, O. E.; Gritsenko, V. A.; Pustovarov, V. A.; Yelisseyev, A. P.; Park, C.; Han, J. H.; Lee, C. J. *Appl. Phys.* **2010**, *108* (1), 013501-4.

(38) Mead, C. A. Phys. Rev. Lett. 1961, 6 (10), 545-546.

(39) Muller, D. A.; Sorsch, T.; Moccio, S.; Baumann, F. H.; Evans-Lutterodt, K.; Timp, G. *Nature* **1999**, *399* (6738), 758–761.

(40) Singh-Bhalla, G.; Du, X.; Hebard, A. F. Appl. Phys. Lett. 2003, 83 (12), 2417-2419.

(41) Bareiss, M.; Hochmeister, A.; Jegert, G.; Zschieschang, U.; Klauk, H.; Huber, R.; Grundler, D.; Porod, W.; Fabel, B.; Scarpa, G.; Lugli, P. J. Appl. Phys. **2011**, 110 (4), 044316–5.

(42) Ben-Sasson, A. J.; Tessler, N. Proc. SPIE 2011, 8117 (1), 81170Z.

(43) Mott, N. F.; Watts-Tobin, R. J. Electrochim. Acta 1961, 4 (2–4), 79–107.

(44) Globerman, O. Lateral And Vertical Organic Field Effect Transistors; Technion—Israel Institute of Technology: Israel, 2006.

(45) Fasolka, M. J.; Mayes, A. M. Annu. Rev. Mater. Res. 2001, 31,

323-355.

(46) Kobayashi, N. P.; Donley, C. L.; Wang, S.-Y.; Williams, R. S. J. Cryst. Growth 2007, 299 (1), 218–222.